Computer Science/Verilog & HW

[Verilog] Basic Concept

mobuk

2023. 2. 1. 13:01

Lexical Conventions ( 어휘 표기법)

- Whitespace

Blank spaces (\n), tabs(\t), and newlines (\n)

- Comments

One line : //

Multiple line : /* */

- Operator

- Unary : operand가 한 개

ex) ~(not)

- Binary : operand가 두 개

ex) &&, +, - …

- Ternary : operand가 세 개

ex) ? :

- Unary : operand가 한 개

- Number Specification

- Sized Number

<size>’<base format><number>

12’habc ⇒ 12bit hexadecimal abc( 4 * 3 )

4’b0000 ⇒ 4 bit binary 0000

- Unsized Number

no <size> and <base format>

23456 ⇒ 32bit

- X or Z values

X : unknown value ( 값이 존재하는데 모르는 것)

12’h13x : 0001 0011 xxxx ( x는 0과 1 아무거나 가능)

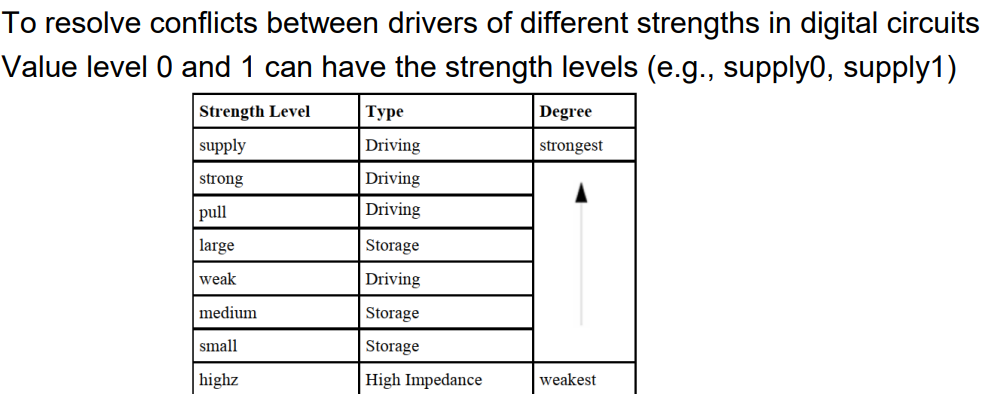

Z : high impedance value ( 값이 없는 것 / HW : 선이 끊어진 것을 의미) - Underscore : 가독성을 위한 밑줄 추가 가능

- Sized Number

- Strings

a sequence of character that are enclosed by double quotes(””)

“Hello verilog”

- Identifiers and Keywords

identifier : names given to objects referenced in designs

keyword : special identifiers reserved to define the language constructs

Data Types

- Value Set

위에서 말했듯이 x는 아직 알지 못하는 것 (0과 1 둘다 가능), z는 불가능한 것을 의미한다.

- Net

declared with the keyword “wire”

connection between hardware element → 진짜 말 그대로 전선을 생각하면 쉽다.

wire a;

wire b, c;

wire d= 1'b0;

- Registers

declared with the keyword “reg”

data storage elements and retain value

reg reset;

initial

begin

reset = 1'b1;

#100 reset = 1'b0;

end

100 times가 지난 시점에 reset 값을 1’b1 → 1’b0 로 변경하고 있다.

Do not confuse the term registers in Verilog with hardware registers

- Vectors ( multiple bit width)

nets or reg data types → vector로 표현 가능

[high# : low#] or [low#:high#]

left number is always MSB of the vector- vector part select

wire [7:0] bus; bus[2:0] bus[0:2] //error

- vectors (cont’d)

[starting_bit - : width] → part-selected decrements from starting

reg [255:0] data1; //little endian

reg [0:255] data2; //big endian

byte = data1[31-:8]; //data[31:24]

byte = data2[31-:8]; //data[24:31]

//선언할 때 endian에 따라 순서가 결정된다.

- integer

general purpose register data type

- real

real register data types are declared with the keyword real

- time

a time data type is used to save simulation time

- arrays

array와 vector는 비슷한 기능을 가지지만 차이점이 있다.

reg [4:0] port_id[0:7]; // 5bit 짜리 reg가 8개

array_4d[0][0][0][0][15:0] = 0; //[15:0] -> part select- Memories

: Memories are modeled as a one-dimensional array of reg - Parameters

constants to be defined in a module by the keyword parameter

Parameters cannot be used as variable.

- local parameters

keyword : localparam

define parameters when their values should not be changed

- local parameters

- String

can be stored in reg

each character in the string takes up 8 bits (1byte)

reg [8 * 18 : 1] string_value;

initial

string_value = "Hello Verilog World";System Tasks

standard system tasks

appear in the form $<keyword>

- display

main system for displaying values of variables // 기본적으로 줄 바꿈을 해줌

$display(p1, p2, p3, ... )

$display("%d", num);- monitor

monitor a signal when its value changes

$monitor($time, "Value of clock : %d " , clock);

//clock의 값이 바뀔 때 마다 출력한다.- Stop

provide to stop during a simulation - finish

terminates the simulation

Compiler Directive

- define

used to define text macros in Verilog

C언어의 #define의 역할과 동일함. - include

include entire contents of a source file in another Verilog file